# HMS30C7110

### **Multipurpose Network Processor**

(ARM Based 32-Bit Microprocessor)

## Datasheet

Version 1.5

MagnaChip Semiconductor Ltd.

#### Copyright. 2002 Magnachip Semiconductor Inc.

ALL RIGHTS RESERVED. No part of this publication may be copied in any form, by photocopy, microfilm, retrieval system, or by any other means now known or hereafter invented without the prior written permission of Magnachip Semiconductor Inc.

Magnachip Semiconductor Inc. #1, Hyangjeong-dong, Heungduk-gu, Cheongju-si, Chungcheonbuk-do, Republic of Korea

Homepage: <u>http://www.Magnachip.com</u>

Technical Support Homepage: will be construction as soon as possible

| H.Q. of Magnachip Semicondu  | Marketing SiteSales in Korea  |                              |  |  |  |  |  |

|------------------------------|-------------------------------|------------------------------|--|--|--|--|--|

| Telephone: 82-(0)43-270-4070 | Telephone: 82-(0)43-270-4085  | Telephone: 82-(0)2-3459-3738 |  |  |  |  |  |

| Facsimile: 82-(0)43-270-4099 | Facsimile: 82-(0)43-270-4099  | Facsimile: 82-(0)2-3459-3945 |  |  |  |  |  |

|                              |                               |                              |  |  |  |  |  |

| World Wide Sales Network     |                               |                              |  |  |  |  |  |

| U.S.A.                       | Taiwan                        | Hong Kong                    |  |  |  |  |  |

| Telephone: 1-408-232-8757    | Telephone: 886-(0)2-2500-8357 | Telephone: 852-2971-1640     |  |  |  |  |  |

| Facsimile: 1-408-232-8135    | Facsimile: 886-(0)2-2509-8977 | Facsimile: 852-2971-1622     |  |  |  |  |  |

|                              |                               |                              |  |  |  |  |  |

HMS30C7110 Datasheet, ver1.5 28 July. 03

Magnachip Semiconductor, Corp. may make changes to specification and product description at any time without notice.

### **Revision History**

| Rev. 0.1  | 2002-07-31 | First draft                                    |  |  |

|-----------|------------|------------------------------------------------|--|--|

| Rev. 1.01 | 2002-10-31 |                                                |  |  |

| Rev. 1.1  | 2002-12-31 |                                                |  |  |

| Rev. 1.2  | 2003-03-17 | Correction on I/O and Register Map             |  |  |

| Rev. 1.3  | 2003-04-13 | Correction on Register Description             |  |  |

| Rev. 1.4  | 2003-07-18 | Correction on Register Description             |  |  |

| Rev. 1.5  | 2003-07-28 | Add I/O Pin Description and add Detail address |  |  |

|           |            | Add PLL register Map                           |  |  |

### Contents

| 1. | Pro  | oduct  | Overview                                       |    |

|----|------|--------|------------------------------------------------|----|

|    | 1.1. |        | Summary of HMS30C7110® features                | 13 |

|    | 1.2. |        | Block Diagram                                  |    |

|    | 1.3. |        | Pin Assignments                                | 17 |

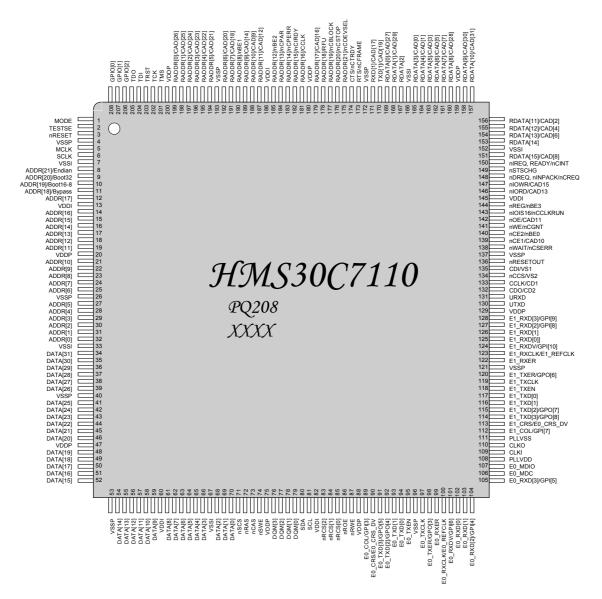

|    | 1.4. |        | Package Pin Diagram (PQ208)                    |    |

|    | 1.5. |        | Pin Description                                |    |

| 2. | Fui  | nction | al Description                                 |    |

|    | 2.1. |        | System Configuration                           |    |

|    |      | 2.1.1. | Power-up Configuration                         |    |

|    |      | 2.1.2. | System Memory Map                              |    |

|    |      | 2.1.3. | Registers Map                                  |    |

|    |      | 2.1.4. | ARM7TDMI Core                                  | 41 |

|    | 2.2. |        | Cache                                          |    |

|    |      | 2.2.1. | Architecture                                   |    |

|    |      | 2.2.2. | User Accessible Registers (Base = 0x1950_0000) |    |

|    | 2.3. |        | Clock/Watchdog Timer                           | 46 |

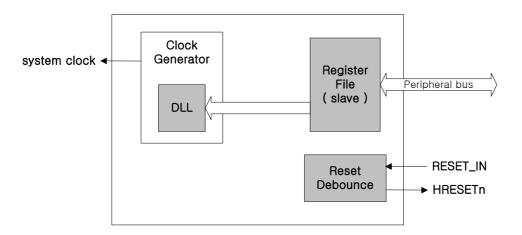

|    |      | 2.3.1. | Block Diagram                                  |    |

|    |      | 2.3.2. | User Accessible Registers (Base = 0x1830_0000) | 47 |

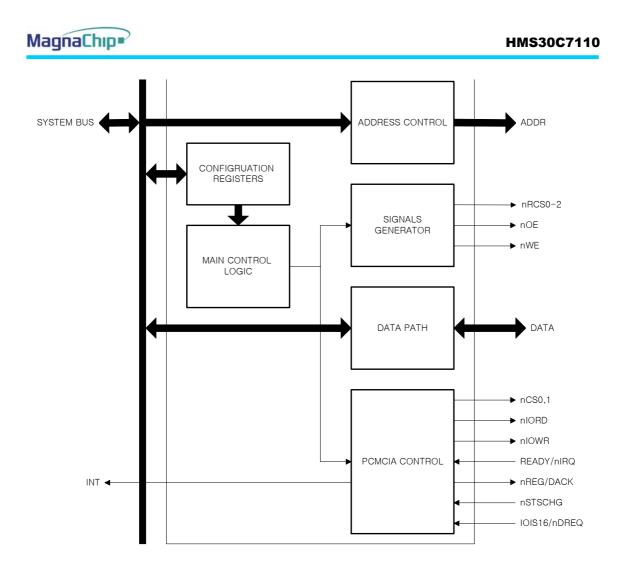

|    | 2.4. |        | Memory Controller (Flash/ROM)                  |    |

|    |      | 2.4.1. | Block Diagram                                  |    |

|    |      | 2.4.2. | User Accessible Registers (Base = 0x1900_0000) | 53 |

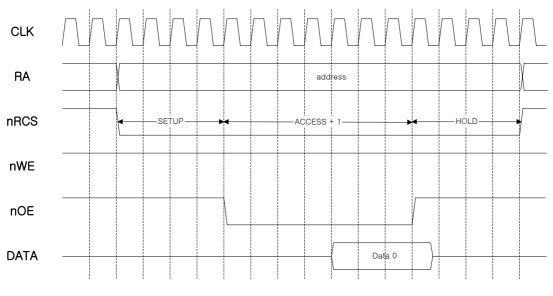

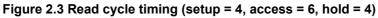

|    |      | 2.4.3. | Timing Diagram                                 |    |

|    | 2.5. |        | Memory Controller (SDRAM)                      |    |

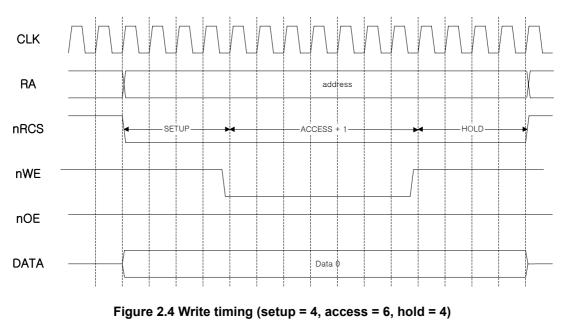

|    |      | 2.5.1. | Block Diagram                                  |    |

|    |      | 2.5.2. | User Accessible Registers (Base = 0x1908_0000) |    |

|    |      | 2.5.3. | Timing Diagram                                 | 63 |

|    | 2.6. |        | Ethernet MAC                                   | 67 |

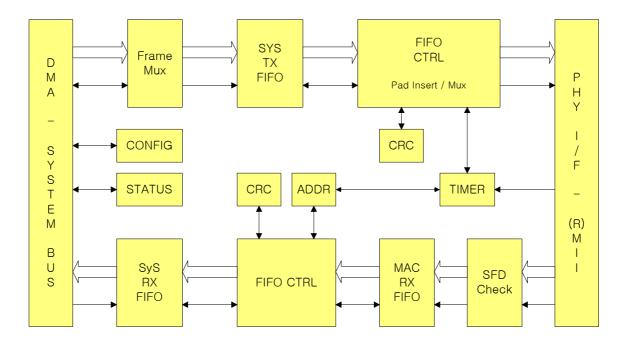

|    |      | 2.6.1. | Block Diagram                                  | 67 |

|    |      |        |                                                |    |

|    | 2.6     | .2.     | User Accessible Registers (Base = 0x1920_0000) | 70  |

|----|---------|---------|------------------------------------------------|-----|

|    | 2.7.    | UA      | RT                                             |     |

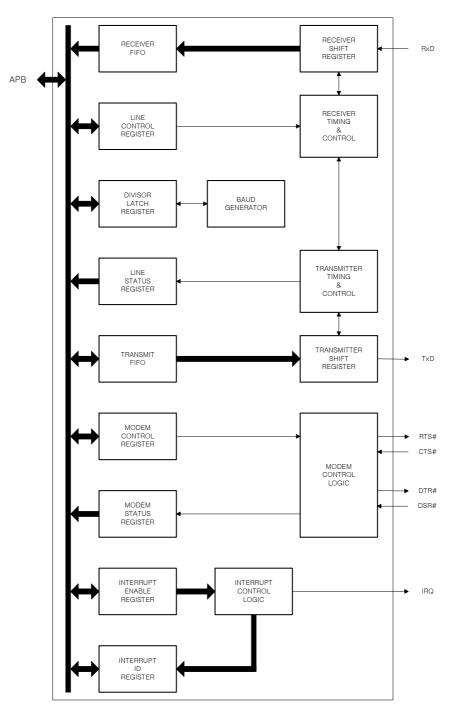

|    | 2.7     | .1.     | Block Diagram                                  |     |

|    | 2.7     | .2.     | User Accessible Registers (Base = 0x1800_0000) |     |

|    | 2.8.    | TIM     | MER                                            |     |

|    | 2.8     | .1.     | User Accessible Registers (Base = 0x1810_0000) |     |

|    | 2.9.    | GPI     | ΙΟ                                             |     |

|    | 2.9     | .1.     | User Accessible Registers (Base = 0x1820_0000) |     |

|    | 2.10.   | SPL     | [                                              |     |

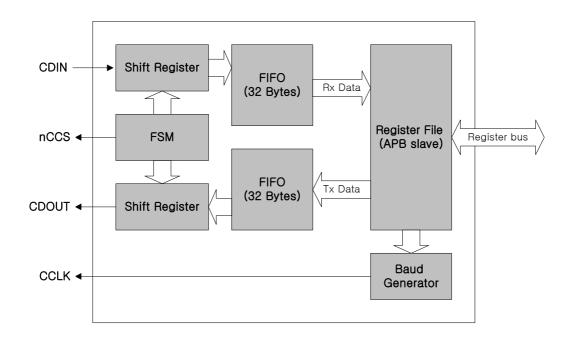

|    | 2.1     | 0.1.    | Block Diagram                                  |     |

|    | 2.1     | 0.2.    | User Accessible Registers (Base = 0x1840_0000) |     |

|    | 2.11.   | DM      | 1A                                             |     |

|    | 2.1     | 1.1.    | User Accessible Registers (Base = 0x1910_0000) |     |

|    | 2.12.   | INT     | ٢C                                             |     |

|    | 2.1     | 2.1.    | User Accessible Registers (Base = 0x1930_0000) |     |

|    | 2.13.   | PCM     | MCIA Controller                                |     |

|    | 2.1     | 3.1.    | User Accessible Registers (Base = 0x1940_0000) |     |

| 3. | Electri | cal Ch  | naracteristics                                 |     |

|    | 3.1.    | Abs     | solute Maximum Ratings                         |     |

|    | 3.2.    | Rec     | commended Operating Conditions                 |     |

|    | 3.3.    | DC      | Characteristics                                |     |

|    | 3.4.    | AC      | Characteristics                                |     |

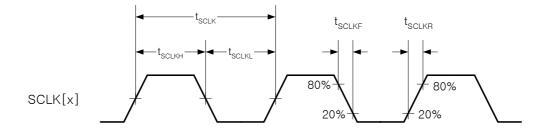

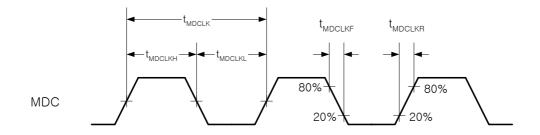

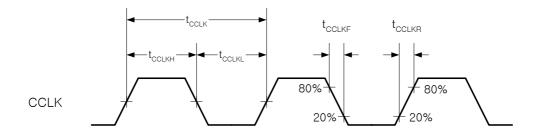

|    | 3.4     | .1.     | Clocks                                         |     |

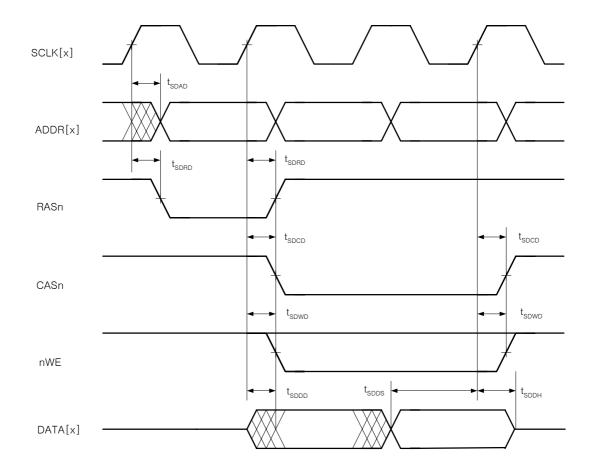

|    | 3.4     | .2.     | SDRAM Timing                                   |     |

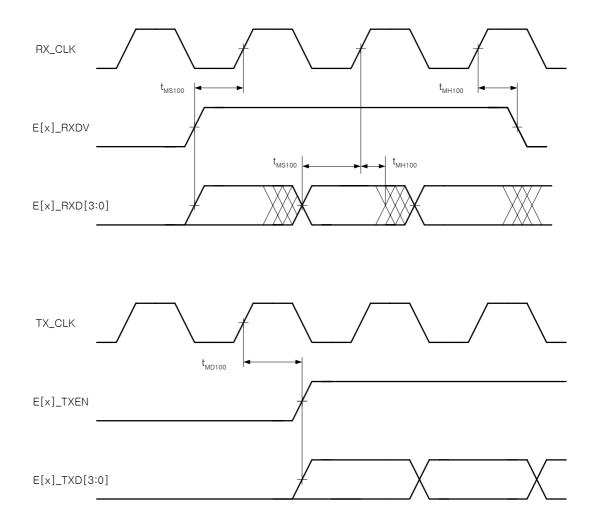

|    | 3.4     | .3.     | Ethernet Timing (MII/100Mbps)                  |     |

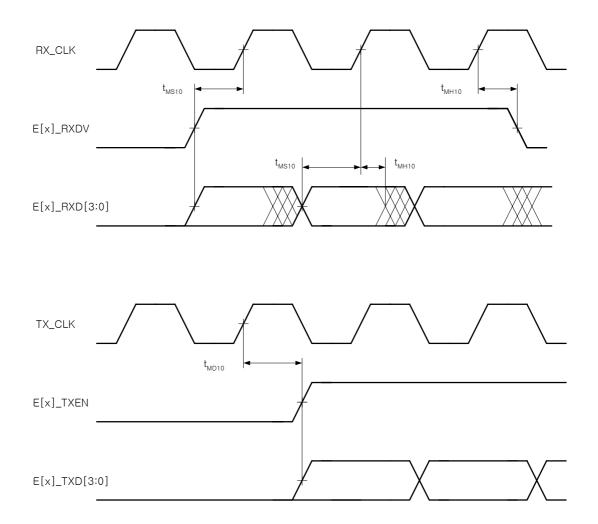

|    | 3.4     | .4.     | Ethernet Timing (MII/10Mbps)                   |     |

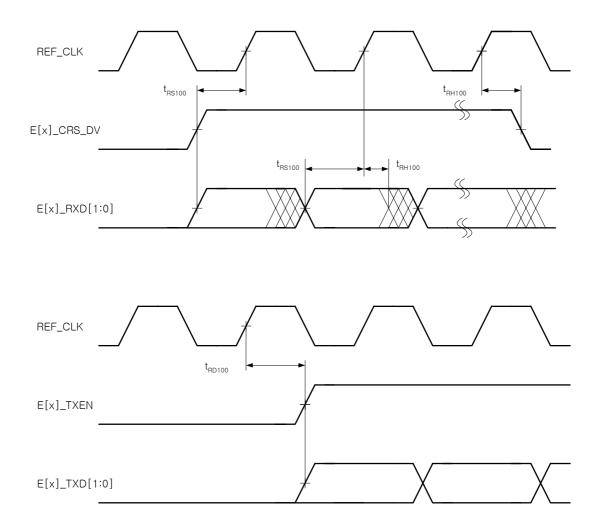

|    | 3.4     | .5.     | Ethernet Timing (RMII)                         | 156 |

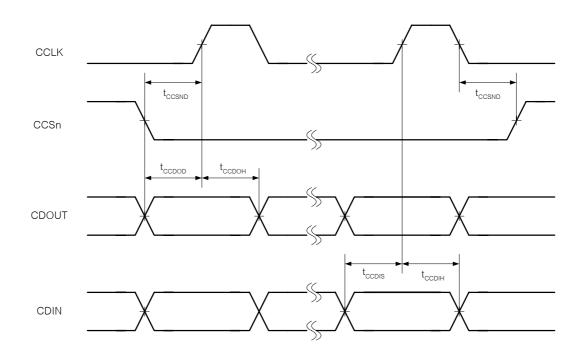

|    | 3.4     | .6.     | SPI Timing                                     |     |

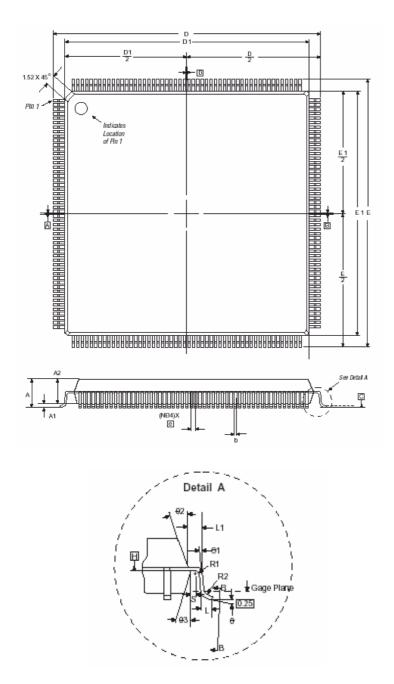

| 4. | Mecha   | nical ( | Characteristics                                |     |

| 5. | Orderi  | ng Inf  | formation                                      |     |

### **Figures**

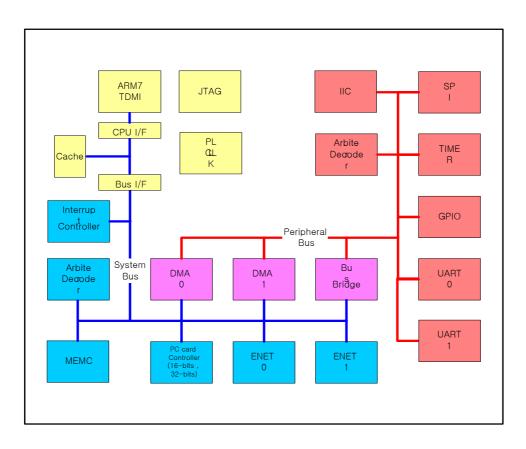

| Figure 1.1 HMS30C7110® Block Diagram                           | 16  |

|----------------------------------------------------------------|-----|

| Figure 1.2 HMS30C7110® 208-Pin PQFP Assignment (top view)      | 25  |

| Figure 2.1 Block Diagram of Clock Module                       | 46  |

| Figure 2.2 Block Diagram of External controller                | 53  |

| Figure 2.3 Read cycle timing (setup = 4, access = 6, hold = 4) | 56  |

| Figure 2.4 Write timing (setup = 4, access = 6, hold = 4)      | 56  |

| Figure 2.5 Block Diagram of SDRAM controller                   | 58  |

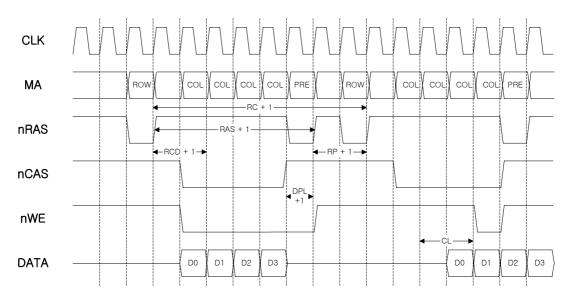

| Figure 2.6 Read/Write cycle                                    | 64  |

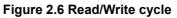

| Figure 2.7 Refresh cycle                                       | 64  |

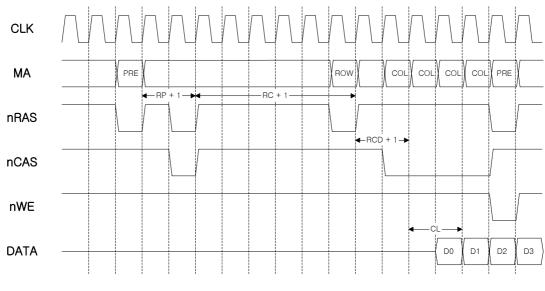

| Figure 2.8 Initialization timing                               | 66  |

| Figure 2.9 Block Diagram of Ethernet MAC                       | 68  |

| Figure 2.10 Block Diagram of UART Device                       | 96  |

| Figure 2.12 Block Diagram of SPI                               | 118 |

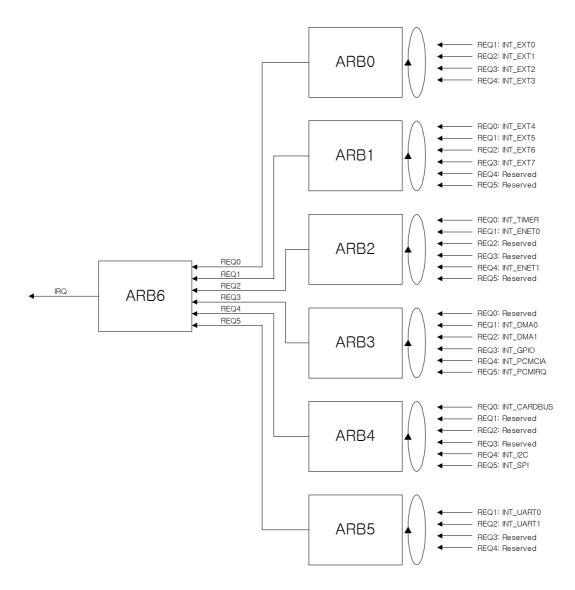

| Figure 2.13 Arbitration Block Diagram                          | 130 |

| Figure 3.1 SDRAM Clock Timing                                  | 152 |

| Figure 3.2 MDC Timing (Ethernet)                               | 152 |

| Figure 3.3 SPI Clock Timing                                    | 152 |

| Figure 3.4 SDRAM Timing Diagram                                | 153 |

| Figure 3.5 Ethernet MII Timing Diagram (100Mbps)               | 154 |

| Figure 3.6 Ethernet MII Timing Diagram (10Mbps)                | 155 |

| Figure 3.7 Ethernet RMII Timing Diagram                        | 156 |

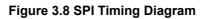

| Figure 3.8 SPI Timing Diagram                                  | 157 |

| Figure 4.1 Mechanical Characteristics                          | 160 |

### **Tables**

| Table 1.1 PQFP Pin List                           | .17  |

|---------------------------------------------------|------|

| Table 1.2 Pin Description                         | .26  |

| Table 2.1 Power-up Configuration                  | . 32 |

| Table 2.2 System Memory Map : SDRAM_REMAP = 0     | . 33 |

| Table 2.3 System Memory Map : SDRAM_REMAP = 1     | .34  |

| Table 2.4 Register Map at AMBA Peri-Bus           | . 35 |

| Table 2.5 Register Map at AMBA Host-Bus           | . 37 |

| Table 2.6 Cache and Write Buffer Control Register | . 42 |

| Table 2.7 Registers for PLL & Watchdog Timer      | .47  |

| Table 2.8 PLL control                             | .47  |

| Table 2.9 Watch Dog Timer control                 | .48  |

| Table 2.10 Watch Dog Timer Interval               | .48  |

| Table 2.11 Main PLL Control                       | . 49 |

| Table 2.12 PLL Status                             | . 50 |

| Table 2.13 Registers for ROM controller           | .54  |

| Table 2.14 Configuration Registers Bit Definition | .54  |

| Table 2.15 Registers for SDRAM controller         | . 59 |

| Table 2.16 Configuration register                 | . 59 |

| Table 2.17 Timing register                        | .60  |

| Table 2.18 Refresh Interval                       | .61  |

| Table 2.19 INIT Control register                  | . 62 |

| Table 2.20 Address Control register               | .63  |

| Table 2.21 Initialization Sequence                | . 65 |

| Table 2.22 Registers for Ethernet MAC             | .71  |

| Table 2.23 MAC Mode Register Bit Definition       | .73  |

| Table 2.24 Interrupt Source Bit Definition        | .75  |

| Table 2.25 Interrupt Enable Bit Definition        | .76  |

| Table 2.26 Inter-Frame Gap Register               | .79  |

| Table 2.27 Collision Configuration Definition     | . 80 |

| Table 2.28 Transmit Buffer Address                | . 80 |

7

| Table 2.29 Transmit Buffer Length                |  |

|--------------------------------------------------|--|

| Table 2.30 Receive Buffer Address                |  |

| Table 2.31 Receive Frame Status                  |  |

| Table 2.32 Receive Buffer Level                  |  |

| Table 2.33 RX Address Return                     |  |

| Table 2.34 Control Mode Register Bit Definition  |  |

| Table 2.35 MII Mode Register Bit Definition      |  |

| Table 2.36 MII Command Register Definition       |  |

| Table 2.37 MII Transmit Data Register            |  |

| Table 2.38 MII Receive Data Register             |  |

| Table 2.39 Length Register                       |  |

| Table 2.40 Multicast Address (Most Significant)  |  |

| Table 2.41 Multicast Address (Least Significant) |  |

| Table 2.42 MAC Address 0 (Control & Byte 5, 4)   |  |

| Table 2.43 MAC Address 1 (Byte 3, 2, 1, 0)       |  |

| Table 2.44 Pause Frame Address 0                 |  |

| Table 2.45 Pause Frame Address 1                 |  |

| Table 2.46 Pause Frame Type ID and OP Code       |  |

| Table 2.47 Pause frame delay value               |  |

| Table 2.48 TX High Priority Queue Base Address   |  |

| Table 2.49 TX High Priority Queue Length         |  |

| Table 2.50 TX Low Priority Queue Level           |  |

| Table 2.51 TX Low Priority Queue Address Return  |  |

| Table 2.52 TX High Priority Queue Level          |  |

| Table 2.53 TX High Priority Queue Address Return |  |

| Table 2.54 Registers for UART                    |  |

| Table 2.55 RHR Bit Definition                    |  |

| Table 2.56 THR Bit Definition                    |  |

| Table 2.57 IER Bit Definition                    |  |

| Table 2.58 IIR Bit Definition                    |  |

| Table 2.59 Interrupt Control Functions           |  |

| Table 2.60 FCR Bit Definition                    |  |

| Table 2.61 LCR Bit Definition                    |  |

#### HMS30C7110

| Table 2.62 MCR Bit Definition                                  |  |

|----------------------------------------------------------------|--|

| Table 2.63 Autoflow Control Configuration                      |  |

| Table 2.64 LSR Bit Definition                                  |  |

| Table 2.65 MSR Bit Definition                                  |  |

| Table 2.66 DLL Bit Definition                                  |  |

| Table 2.67 DLM Bit Definition                                  |  |

| Table 2.68 Registers for TIMER                                 |  |

| Table 2.69 Clock Selection Register Bit Definition             |  |

| Table 2.70 Timer Control Register Bit Definition               |  |

| Table 2.71 Timer Interval Register Bit Definition              |  |

| Table 2.72 Current Timer Value Register Bit Definition         |  |

| Table 2.73 Interrupt Source Register Bit Definition            |  |

| Table 2.74 Interrupt Enable                                    |  |

| Table 2.75 Registers for GPIO                                  |  |

| Table 2.76 GPO Data Register Bit Definition                    |  |

| Table 2.77 GPI Data Register Bit Definition                    |  |

| Table 2.78 GPIO Direction Register Bit Definition              |  |

| Table 2.79 Interrupt Source Register Bit Definition            |  |

| Table 2.80 The Bit Definition of the Interrupt Enable Register |  |

| Table 2.81 Interrupt Mode Register Bit Definition              |  |

| Table 2.82 Interrupt Level Register Bit Definition             |  |

| Table 2.89 Registers for SPI                                   |  |

| Table 2.90 SPI Control Register Bit Definition                 |  |

| Table 2.91 Configuration Register Bit Definition               |  |

| Table 2.92 Tx Data Register Bit Definition                     |  |

| Table 2.93 Rx Data Register Bit Definition                     |  |

| Table 2.94 Interrupt Source Register Bit Definition            |  |

| Table 2.95 Interrupt Mask Register Bit Definition              |  |

| Table 2.96 SPI Status Register Bit Definition                  |  |

| Table 2.97 DMA Initial Source Register                         |  |

| Table 2.98 DMA Initial Destination Register                    |  |

| Table 2.99 DMA Control Register                                |  |

| Table 2.100 DMA Status Register                                |  |

9

| Table 2.101 DMA Mask Trigger Register               | . 126 |

|-----------------------------------------------------|-------|

| Table 2.102 Interrupt Source Register               | . 129 |

| Table 2.103 Source Pending Register                 | . 132 |

| Table 2.104 Interrupt Mode Register                 | . 133 |

| Table 2.105 Interrupt Mask Register                 | . 133 |

| Table 2.106 Priority Register                       | . 134 |

| Table 2.107 Interrupt Pending Register              | . 135 |

| Table 2.108 Interrupt Offset Register               | . 136 |

| Table 2.109 Registers for PCMCIA                    | . 137 |

| Table 2.110 Registers for CardBus                   | . 138 |

| Table 2.111 IDR Bit Definition                      | . 138 |

| Table 2.112 ISR Bit Definition                      | . 139 |

| Table 2.113 ICR Bit Definition                      | . 139 |

| Table 2.114 GCR Bit Definition                      | . 140 |

| Table 2.115 CSCR Bit Definition                     | . 141 |

| Table 2.116 IER Bit Definition                      | . 141 |

| Table 2.117 Setup Bit Definition                    | . 142 |

| Table 2.118 Command Bit Definition                  | . 142 |

| Table 2.119 Recovery Bit Definition                 | . 143 |

| Table 2.120 Start Address Bit Definition            | . 144 |

| Table 2.121 End Address Bit Definition              | . 144 |

| Table 2.122 GPIO direction registers Bit Definition | . 145 |

| Table 2.123 GPO registers Bit Definition            | . 145 |

| Table 2.124 GPI registers Bit Definition            | . 145 |

| Table 2.125 GPIO muxing table                       | . 146 |

| Table 2.126 Command Bit Definition                  | . 147 |

| Table 2.127 Status Bit Definition                   | . 148 |

| Table 2.128 Retry time register Bit Definition      | . 149 |

| Table 2.129 Clk select register Bit Definition      | . 149 |

| Table 3.1 Absolute maximum ratings                  | . 150 |

| Table 3.2 Recommended operating conditions          | . 150 |

| Table 3.3 DC Characteristics                        | . 151 |

| Table 3.4 A.C. Electrical Characteristics           | . 158 |

### **1. Product Overview**

The HMS30C7110® is a low-cost and high performance network processor for telecommunication equipments such as IP sharer, Wireless Local Area Network Access Point (WLAN-AP), Managed switch/Bridge/Hub, routers, and other devices that provide high-speed data networking. The HMS30C7110® includes an ARM7TDMI processor with unified cache, and common network functions such as dual Ethernet MAC, PCMCIA, and other common peripherals.

### 1.1. Summary of HMS30C7110® features

#### System

- 32-bit ARM7 Processor Core with cache

- High Speed System Bus & Peripheral Bus

- Supports both Big-Endian / Little-Endian modes

- JTAG-based debug solution

#### Cache

- 4K Byte unified (data + instruction)

- 4-way set associative

- Write back policy

- Read miss fill up

- 8 word write buffer

#### Ethernet MAC

- Dual MAC with 10/100Base T

- MII, RMII and 7-wire interface

- 8 Ethernet MAC addresses

- Internal loop-back mode

- Allows programming of PHY active level signal

- Pad insertion for minimum frame size (64 bytes)

- Programmable maximum frame length (up to 2000 bytes)

#### **DMA Controller**

- 2-channel programmable DMA

- UART DMA support

#### UART

- Independent 2-channel Tx/Rx

- Full duplex mode

- Hardware flow control for one channel

- 16 byte internal Rx/Tx FIFOs to reduce data latency

- Even, odd, forced one, and forced zero parity mode

#### Interrupt Controller

- Handles up to 32 interrupt sources

- Supports hardware priority function

- Programmable IRQ/FIQ mode

#### SPI

- Operates as master mode

- Configurable address and data width

#### Timer

- Three channels of 32-bit timer

- Selectable channel clock speed

#### GPIO

- Up to 13 GPI, 9 GPO (General Purpose Input Output) ports

- Supports external interrupt inputs

#### **Memory Controller**

- Supports up to three 4MB banks (Flash/ROM) and one 128MB bank (SDRAM)

- Supports all major SDRAM/ROM/Flash memories

- Supports 32-bit data width for SDRAM

- Supports 8-bit, 16-bit, and 32-bit data width for Flash/ROM

#### **PCMCIA** Controller

- Supports 16-bit PC Card host interface

- Supports CardBus

Note: 16-bit PCMCIA is designated as "16-bit PC Card" and 32-bit PCMCIA as "CardBus". PC card is the card suitable for insertion in PCMCIA slot.

#### **Physical Characteristics**

- Operating Voltage: Core 2.5V, I/O 3.3V

- Technology: 0.25um CMOS

- Operating Temperature: 0 ~ 70° C

- Operating Frequency: 70 MHz

- Package Type: 208 PQFP

### 1.2. Block Diagram

Figure 1.1 HMS30C7110® Block Diagram

### 1.3. Pin Assignments

| Pin # | Pin Name        | 10 | Pad    | Description                                                                 |                 |                                   |                           |

|-------|-----------------|----|--------|-----------------------------------------------------------------------------|-----------------|-----------------------------------|---------------------------|

|       |                 |    | Туре   |                                                                             |                 |                                   |                           |

| 1     | MODE            | I  | PICD   | Operation Mode                                                              |                 |                                   |                           |

|       |                 |    |        | MODE                                                                        | TESTSE          | Contents                          |                           |

|       |                 |    |        | 0                                                                           | 0               | Normal Operation                  |                           |

|       |                 |    |        | 0                                                                           | 1               | NANDTREE/BIST/PLL Test            |                           |

|       |                 |    |        | 1                                                                           | 0               | Parallel Capture for ATPG         |                           |

|       |                 |    |        | 1                                                                           | 1               | Scan Shift for ATPG               |                           |

| 2     | TESTSE          | Ι  | PICD   | Test Scan E                                                                 | Enable. Refe    | to the description for Pin 1      |                           |

| 3     | nRESET          | Ι  | PICS   | System Res                                                                  | set, active lov | N                                 |                           |

| 4     | VSSP            | Р  |        | VSS for IO                                                                  |                 |                                   |                           |

| 5     | MCLK            | Ι  | PICS   | SDRAM Me                                                                    | emory Feedb     | ack Clock                         |                           |

| 6     | SCLK            | 0  | POC8A  | SDRAM clo                                                                   | ock             |                                   |                           |

| 7     | VSSI            | Р  |        | VSS for cor                                                                 | e               |                                   |                           |

| 8     | ADDR21/Endian   | BD | PBCD8A | D8A Address Bus/Endian at Reset period Pulled down internally over 50 Kohm. |                 |                                   |                           |

|       |                 |    |        | 0: Little Endian (Default)                                                  |                 |                                   |                           |

|       |                 |    |        | 1: Big Endian                                                               |                 |                                   |                           |

| 9     | ADDR20/Boot32   | BD | PBCD8A | Address Bu                                                                  | s/Boot32 at     | Reset period. Pulled down inter   | nally over 50 Kohm.       |

|       |                 |    |        | 0: 16-bit bo                                                                | oting(Default   | )                                 |                           |

|       |                 |    |        | 1: 32-bit bo                                                                | oting           |                                   |                           |

| 10    | ADDR19/Boot16-8 | BU | PBCU8A | Address Bu                                                                  | is/Boot16-8 a   | at Reset. Pulled up internally ov | er 50 Kohm.               |

|       |                 |    |        | 0: 8-bit boo                                                                | ting            |                                   |                           |

|       |                 |    |        | 1: 16-bit booting(Default)                                                  |                 |                                   |                           |

| 11    | ADDR18/Bypass   | BU | PBCU8A | Address Bu                                                                  | is/Bypass Inf   | ternal Power-On-Reset Circuit.    | Pulled up internally over |

|       |                 |    |        | 50 Kohm.                                                                    | The active o    | utput width is over 1.5 Sec wh    | nen 10MHz main clock is   |

|       |                 |    |        | used.                                                                       |                 |                                   |                           |

|       |                 |    |        | 0: Use internal Power-On-Reset ciruit                                       |                 |                                   |                           |

|       |                 |    |        | 1: Bypass ir                                                                | nternal Powe    | r-On-Reset circuit (Default)      |                           |

#### Table 1.1 PQFP Pin List

© 2003 MagnaChip Semiconductor Ltd. All Rights Reserved

17

|    |            |    |        | Dravida automal 40 Kahm auto da una internal DEOET       |

|----|------------|----|--------|----------------------------------------------------------|

|    |            |    |        | Provide external 10 Kohm pull-down to use internal RESET |

| 12 | ADDR17     | 0  | POC8A  | Address Bus                                              |

| 13 | VCCI       | Р  |        | VDD for core                                             |

| 14 | ADDR16     | 0  | POC8A  | Address Bus                                              |

| 15 | ADDR15     | 0  | POC8A  | Address Bus                                              |

| 16 | ADDR14/BA1 | 0  | POC8A  | Address Bus/SDRAM Bank Address 1                         |

| 17 | ADDR13/BA0 | 0  | POC8A  | Address Bus/SDRAM Bank Address 0                         |

| 18 | ADDR12     | 0  | POC8A  | Address Bus                                              |

| 19 | ADDR11     | 0  | POC8A  | Address Bus                                              |

| 20 | VCCP       | Р  |        | VDD for IO                                               |

| 21 | ADDR10     | 0  | POC8A  | Address Bus                                              |

| 22 | ADDR9      | 0  | POC8A  | Address Bus                                              |

| 23 | ADDR8      | 0  | POC8A  | Address Bus                                              |

| 24 | ADDR7      | 0  | POC8A  | Address Bus                                              |

| 25 | ADDR6      | 0  | POC8A  | Address Bus                                              |

| 26 | VSSP       | Р  |        | VSS for IO                                               |

| 27 | ADDR5      | 0  | POC8A  | Address Bus                                              |

| 28 | ADDR4      | 0  | POC8A  | Address Bus                                              |

| 29 | ADDR3      | 0  | POC8A  | Address Bus                                              |

| 30 | ADDR2      | 0  | POC8A  | Address Bus                                              |

| 31 | ADDR1      | 0  | POC8A  | Address Bus                                              |

| 32 | ADDR0      | 0  | POC8A  | Address Bus                                              |

| 33 | VSSI       | Р  |        | VSS for core                                             |

| 34 | DATA31     | BU | PBCU8A | Data Bus                                                 |

| 35 | DATA30     | BU | PBCU8A | Data Bus                                                 |

| 36 | DATA29     | BU | PBCU8A | Data Bus                                                 |

| 37 | DATA28     | BU | PBCU8A | Data Bus                                                 |

| 38 | DATA27     | BU | PBCU8A | Data Bus                                                 |

| 39 | DATA26     | BU | PBCU8A | Data Bus                                                 |

| 40 | VSSP       | Р  |        | VSS for IO                                               |

| 41 | DATA25     | BU | PBCU8A | Data Bus                                                 |

| 42 | DATA24     | BU | PBCU8A | Data Bus                                                 |

| 42 | DATA 22 | БП | DDCU0A | Data Dua              |

|----|---------|----|--------|-----------------------|

| 43 | DATA23  | BU | PBCU8A | Data Bus              |

| 44 | DATA22  | BU | PBCU8A | Data Bus              |

| 45 | DATA21  | BU | PBCU8A | Data Bus              |

| 46 | DATA20  | BU | PBCU8A | Data Bus              |

| 47 | VCCP    | Р  |        | VDD for IO            |

| 48 | DATA19  | BU | PBCU8A | Data Bus              |

| 49 | DATA18  | BU | PBCU8A | Data Bus              |

| 50 | DATA17  | BU | PBCU8A | Data Bus              |

| 51 | DATA16  | BU | PBCU8A | Data Bus              |

| 52 | DATA15  | BU | PBCU8A | Data Bus              |

| 53 | VSSP    | Р  |        | VSS for IO            |

| 54 | DATA14  | BU | PBCU8A | Data Bus              |

| 55 | DATA13  | BU | PBCU8A | Data Bus              |

| 56 | DATA12  | BU | PBCU8A | Data Bus              |

| 57 | DATA11  | BU | PBCU8A | Data Bus              |

| 58 | DATA10  | BU | PBCU8A | Data Bus              |

| 59 | DATA9   | BU | PBCU8A | Data Bus              |

| 60 | VCCI    | Р  |        | VDD for core          |

| 61 | DATA8   | BU | PBCU8A | Data Bus              |

| 62 | DATA7   | BU | PBCU8A | Data Bus              |

| 63 | DATA6   | BU | PBCU8A | Data Bus              |

| 64 | DATA5   | BU | PBCU8A | Data Bus              |

| 65 | DATA4   | BU | PBCU8A | Data Bus              |

| 66 | DATA3   | BU | PBCU8A | Data Bus              |

| 67 | VSSI    | Р  |        | VSS for core          |

| 68 | DATA2   | BU | PBCU8A | Data Bus              |

| 69 | DATA1   | BU | PBCU8A | Data Bus              |

| 70 | DATA0   | BU | PBCU8A | Data Bus              |

| 71 | nSCS    | 0  | POC8A  | SDRAM Chip Select     |

| 72 | nRAS    | 0  | POC8A  | Row Address Strobe    |

| 73 | nCAS    | 0  | POC8A  | Column Address Strobe |

| 74 | nSWE    | 0  | POC8A  | SDRAM Write Enable    |

| 75  | VCCP             | Р |       | VDD for IO                                      |

|-----|------------------|---|-------|-------------------------------------------------|

| 76  | DQM3             | 0 | POC8A | SDRAM Data Mask 3                               |

| 77  | DQM2             | 0 | POC8A | SDRAM Data Mask 2                               |

| 78  | DQM1             | 0 | POC8A | SDRAM Data Mask 1                               |

| 79  | DQM0             | 0 | POC8A | SDRAM Data Mask 0                               |

| 80  | GPI[11]          | В | PBC4A | GPIO input bit 11                               |

| 81  | GPI[12]          | В | PBC4A | GPIO input bit 12                               |

| 82  | VCCI             | Р |       | VDD for core                                    |

| 83  | nRCS2            | 0 | POC4A | ROM/FLASH Chip Select                           |

| 84  | nRCS1            | 0 | POC4A | ROM/FLASH Chip Select                           |

| 85  | nRCS0            | 0 | POC4A | ROM/FLASH Chip Select                           |

| 86  | nROE             | 0 | POC8A | ROM/FLASH Output Enable                         |

| 87  | nRWE             | 0 | POC8A | ROM/FLASH Write Enable                          |

| 88  | VCCP             | Р |       | VDD for IO                                      |

| 89  | E0_COL/ /GPI[3]  | I | PIC   | Collision/GPI[3]                                |

| 90  | E0_CRS/E0_CRSDV  | Ι | PIC   | Carrier Sense from the Ethernet PHY             |

| 91  | E0_TXD3/ GPO[5]  | 0 | POC4A | Transmit Data from the Ethernet PHY/GPO[5]      |

| 92  | E0_TXD2/GPO[4]   | 0 | POC4A | Transmit Data from the Ethernet PHY/GPO[4]      |

| 93  | E0_TXD1/ E0_TXD1 | 0 | POC4A | Transmit Data from the Ethernet PHY/            |

| 94  | E0_TXD0/ E0_TXD0 | 0 | POC4A | Transmit Data from the Ethernet PHY             |

| 95  | E0_TXEN/ E0_TXEN | 0 | POC4A | Transmit Data Enable to the Ethernet PHY        |

| 96  | VSSP             | Р |       | VSS for IO                                      |

| 97  | E0_TXCLK         | Η | PICS  | Transmit Clock from the Ethernet PHY            |

| 98  | E0_TXER/ GPO[3]  | 0 | POC4A | Transmit Data Error to the Ethernet PHY/GPO[3]  |

| 99  | E0_RXER/ E0_RXER | Ι | PIC   | Receive Data Error from the Ethernet PHY        |

| 100 | E0_RXCLK/E0_CLK  | Η | PICS  | Receive Clock from the Ethernet PHY             |

| 101 | E0_RXDV/ GPI[6]  | Ι | PIC   | Receive Data Valid from the Ethernet PHY/GPI[6] |

| 102 | E0_RXD0 /E0_RXD0 | Ι | PIC   | Receive Data from the Ethernet PHY              |

| 103 | E0_RXD1/E0_RXD1  | Ι | PIC   | Receive Data from the Ethernet PHY              |

| 104 | E0_RXD2/ GPI[4]  | I | PIC   | Receive Data from the Ethernet PHY/GPI[4]       |

| 105 | E0_RXD3/ GPI[5]  | - | PIC   | Receive Data from the Ethernet PHY/GPI[5]       |

| 106 | E0_MDC           | 0 | POC4A | Receive Data from the Ethernet PHY              |

#### HMS30C7110

| 107 | E0_MDIO          | В  | PBCC4A | Receive Data from the Ethernet PHY               |

|-----|------------------|----|--------|--------------------------------------------------|

| 108 | <br>PLLVCC       | Р  |        | VDD for PLL                                      |

| 109 | CLKI             | 1  | POSC1  | Main Clock In for crystal (10~20MHz)             |

| 110 | CLKO             | 0  | POSC1  | Main Clock Out for crystal (10~20MHz)            |

| 111 | PLLVSS           | Р  |        | VSS for PLL                                      |

| 112 | E1_COL/ GPI[7]   | 1  | PIC    | Collision/GPI[7]                                 |

| 113 | E1_CRS/E1_CRSDV  | 1  | PIC    | Carrier Sense from the Ethernet PHY              |

| 114 | E1_TXD3/ GPO[8]  | 0  | POC4A  | Transmit Data from the Ethernet PHY/GPO[8]       |

| 115 | E1_TXD2/ GPO[7]  | 0  | POC4A  | Transmit Data from the Ethernet PHY/GPO[7]       |

| 116 | E1_TXD1/ E1_TXD1 | 0  | POC4A  | Transmit Data from the Ethernet PHY              |

| 117 | E1_TXD0/ E1_TXD0 | 0  | POC4A  | Transmit Data from the Ethernet PHY              |

| 118 | E1_TXEN/ E1_TXEN | 0  | POC4A  | Transmit Data Enable to the Ethernet PHY         |

| 119 | E1_TXCLK         | I  | PICS   | Transmit Clock from the Ethernet PHY             |

| 120 | E1_TXER/ GPO[6]  | 0  | POC4A  | Transmit Data Error to the Ethernet PHY/GPO[6]   |

| 121 | VSSP             | Р  |        | VSS for IO                                       |

| 122 | E1_RXER/ E1_RXER | I  | PIC    | Receive Data Error from the Ethernet PHY         |

| 123 | E1_RXCLK/ E1_CLK | I  | PICS   | Receive Clock from the Ethernet PHY              |

| 124 | E1_RXDV/ GPI[10] | Ι  | PIC    | Receive Data Valid from the Ethernet PHY/GPI[10] |

| 125 | E1_RXD0/ E1_RXD0 | Ι  | PIC    | Receive Data from the Ethernet PHY               |

| 126 | E1_RXD1/E1_RXD1  | Ι  | PIC    | Receive Data from the Ethernet PHY               |

| 127 | E1_RXD2/ GPI[8]  | I  | PIC    | Receive Data from the Ethernet PHY/GPI[8]        |

| 128 | E1_RXD3/ GPI[9]  | I  | PIC    | Receive Data from the Ethernet PHY/GPI[9]        |

| 129 | VCCP             | Ρ  |        | VDD for IO                                       |

| 130 | UTXD             | 0  | POC4A  | UART channel Tx Data                             |

| 131 | URXD             | Ι  | PIC    | UART channel Rx Data                             |

| 132 | nCCD_02/CDO      | В  | PBC4A  | CD1 input/ SPI Data Output                       |

| 133 | nCCD_01/CCLK     | В  | PBC4A  | CD2 input/ SPI Clock Output                      |

| 134 | CVS2/nCCS        | В  | PBC4A  | VS 1/ SPI Chip Select                            |

| 135 | CVS1/CDI         | В  | PBC4A  | VS 1/ SPI Data Input                             |

| 136 | RESET_nCRST      | 0  | POC8A  | Card Reset                                       |

| 137 | VSSP             | Ρ  |        | VSS for IO                                       |

| 138 | nWAIT_nCSERR/RxD | BU | PBCU4A | Wait from 16-bit PC Card / RxData for UART 1     |

21

|     |                    |    | -      |                                                                           |

|-----|--------------------|----|--------|---------------------------------------------------------------------------|

| 139 | nCE2_CAD10         | BU | PBCU4A | Chip enable 0 for 16-bit PC Card/CardBus Address Data                     |

| 140 | nCE1_nCBE0         | BU | PBCU4A | Chip enable for 16-bit PC Card/CardBus CBE0                               |

| 141 | nWE_nCGNT          | BU | PBCU4A | Write enable for 16-bit PC Card /CardBus CGNT                             |

| 142 | nOE_CAD11          | BU | PBCU4A | Read enable for 16-bit PC Card /CardBus Address Data                      |

| 143 | WP/nIOIS16_nCCLKRU | BU | PBCU4A | Write Protect / IO Size 16 (*DMA Request for IO mode 3)/CardBus CCLKRUN   |

|     | Ν                  |    |        |                                                                           |

| 144 | nREG_nCBE3 / DACK  | BU | PBCU4A | Attribute Memory Select for 16-bit PC Card / DMA Acknowledge              |

| 145 | VCCI               | Р  |        | VDD for core                                                              |

| 146 | nIORD_CAD13        | BU | PBCU4A | I/O Read for 16-bit PC Card /CardBus Address Data                         |

| 147 | nIOWR_CAD15        | BU | PBCU4A | I/O Write for 16-bit PC Card /CardBus Address Data                        |

| 148 | nINPACK_nCREQ      | BU | PBCU4A | Input Acknowledge for 16-bit PC Card (*DMA Request for IO mode 2)/CardBus |

|     |                    |    |        | CREQ                                                                      |

| 149 | nSTSCHG_CSTSCHG    | BU | PBCU4A | Status Change from 16-bit PC Card / CTS for UART 1                        |

| 150 | READY/nIREQ_nCINT  | BU | PBCU4A | Initialization Ready from 16-bit PC Card/CardBus Interrupt Request        |

| 151 | D15_CAD8           | BU | PBCU4A | 16-bit PC CARD Data/CardBus Address Data                                  |

| 152 | VSSI               | Р  |        | VSS for core                                                              |

| 153 | D14                | BU | PBCU4A | 16-bit PC CARD Data                                                       |

| 154 | D13_CAD6           | BU | PBCU4A | 16-bit PC CARD Data/CardBus Address Data                                  |

| 155 | D12_CAD4           | BU | PBCU4A | 16-bit PC CARD Data/CardBus Address Data                                  |

| 156 | D11_CAD2           | BU | PBCU4A | 16-bit PC CARD Data/CardBus Address Data                                  |

| 157 | D10_CAD31          | BU | PBCU4A | 16-bit PC CARD Data/CardBus Address Data                                  |

| 158 | D9_CAD30           | BU | PBCU4A | 16-bit PC CARD Data/CardBus Address Data                                  |

| 159 | VCCP               | Р  |        | VDD for IO                                                                |

| 160 | D8_CAD28           | BU | PBCU4A | 16-bit PC CARD Data/CardBus Address Data                                  |

| 161 | D7_CAD7            | BU | PBCU4A | 16-bit PC CARD Data/CardBus Address Data                                  |

| 162 | D6_CAD5            | BU | PBCU4A | 16-bit PC CARD Data/CardBus Address Data                                  |

| 163 | D5_CAD3            | BU | PBCU4A | 16-bit PC CARD Data/CardBus Address Data                                  |

| 164 | D4_CAD1            | BU | PBCU4A | 16-bit PC CARD Data/CardBus Address Data                                  |

| 165 | D3_CAD0            | BU | PBCU4A | 16-bit PC CARD Data/CardBus Address Data                                  |

| 166 | VSSI               | Р  |        | VSS for core                                                              |

| 167 | D2                 | BU | PBCU4A | 16-bit PC CARD Data                                                       |

| 168 | D1_CAD29           | BU | PBCU4A | 16-bit PC CARD Data/CardBus Address Data                                  |

|     |                    |    |        |                                                                           |

| 148DD_CAD27BUPBCU4A16-bit PC CARD Data/CardBus Address Data170AA5_CAD197TXD1BUPPCU4A16-bit PC Card Address/CardBus Address Data / TxData for UART 1171AA4_CAD17BUPBCU4A16-bit PC Card Address/CardBus Address Data172AZ3_nCFRAMBUPBCU4A16-bit PC Card Address/CardBus Frame173AZ3_nCFRDVBUPBCU4A16-bit PC Card Address/CardBus Dev Sel174AZ2_nCTRDVBUPBCU4A16-bit PC Card Address/CardBus Dev Sel175AA1_nCELCCKBUPBCU4A16-bit PC Card Address/CardBus Dev Sel176AA2n_CSTDPBUPBCU4A16-bit PC Card Address/CardBus Dev Sel177AA1_nCELCCKBUPBCU4A16-bit PC Card Address/CardBus Dev Sel178AA1_nCELCCKBUPBCU4A16-bit PC Card Address/CardBus Address Data179AA1_nCELCCKBUPBCU4A16-bit PC Card Address/CardBus Address Data180AV1_CCPPVD for IO181AA15_nCIRDVBUPBCU4A16-bit PC Card Address/CRPV183AA1_nCPERRBUPBCU4A16-bit PC Card Address/CRPX184AA1_nCPERRBUPBCU4A16-bit PC Card Address/CardBus Address Data185AA1_nCAD12BUPBCU4A16-bit PC Card Address/CardBus Address Data186AA1_nCAD12BUPBCU4A16-bit PC Card Address/CardBus Address Data187AA1_CAD2BUPBCU4A16-bit PC Card Address/CardBus Address Data18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |                |    | -      |                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------|----|--------|-----------------------------------------------------------------|

| Image: Construction         Image: Construction         Image: Construction         Image: Construction           171         A23_nCFRAME         BU         PBCU4A         16-bit PC Card Address/CardBus Frame           172         A23_nCFRAME         BU         PBCU4A         16-bit PC Card Address/CardBus Frame           173         A21_nCDEVSEL         BU         PBCU4A         16-bit PC Card Address/CardBus Dev Sel           176         A20_nCSTOP         BU         PBCU4A         16-bit PC Card Address/CardBus STOP           177         A19_nCBLOCK         BU         PBCU4A         16-bit PC Card Address/CardBus Address Data           178         A18         B         PBCU4A         16-bit PC Card Address/CardBus Address Data           178         A19_nCBLOCK         BU         PBCU4A         16-bit PC Card Address/CardBus Address Data           179         A17_CAD16         BU         PBCU4A         16-bit PC Card Address/CardBus Address Data           180         VCCD         P         VDD for 10         VDD for 10           181         A16_CCLK         BU         PBCU4A         16-bit PC Card Address/CPERR           182         A14_nCPERR         BU         PBCU4A         16-bit PC Card Address/CardBus Address Data           183         A12_nCCBE2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 169 | D0_CAD27       | BU | PBCU4A | 16-bit PC CARD Data/CardBus Address Data                        |

| NSSP         P         VSS for IO           173         A23_nCFRAME         BU         PBCU4A         16-bit PC Card Address/CardBus Frame           174         A22_nCTRDY         BU         PBCU4A         16-bit PC Card Address/CardBus TRDY           175         A21_nCDEVSEL         BU         PBCU4A         16-bit PC Card Address/CardBus Dev Sel           176         A20_nCSTOP         BU         PBCU4A         16-bit PC Card Address/CardBus CBLOCK           177         A19_nCBLOCK         BU         PBCU4A         16-bit PC Card Address/CardBus CBLOCK           178         A17_CAD16         BU         PBCU4A         16-bit PC Card Address/CardBus Address Data           179         A17_CAD16         BU         PBCU4A         16-bit PC Card Address/CLK           180         VCCP         P         VDD for IO           181         A16_nCRPY         BU         PBCU4A         16-bit PC Card Address/CLK           182         A15_nCIRPY         BU         PBCU4A         16-bit PC Card Address/CLK           183         A14_nCPERR         BU         PBCU4A         16-bit PC Card Address/CRBY           184         A13_cPAR         BU         PBCU4A         16-bit PC Card Address/CardBus Address Data           185         A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 170 | A25_CAD19/TXD1 | BU | PBCU4A | 16-bit Pc Card Address/CardBus Address Data / TxData for UART 1 |

| A23_nCFRAMEBUPBCU4A16-bit PC Card Address/CardBus Frame174A22_nCTRDYBUPBCU4A16-bit PC Card Address/CardBus TRDY175A21_nCDEVSELBUPBCU4A16-bit PC Card Address/CardBus Dev Sel176A20_nCSTOPBUPBCU4A16-bit PC Card Address/CardBus CBLOCK177A19_nCBLOCKBUPBCU4A16-bit PC Card Address/CardBus CBLOCK178A19_nCBLOCKBUPBCU4A16-bit PC Card Address/CardBus Address Data179A17_CAD16BUPBCU4A16-bit PC Card Address/CardBus Address Data180VCCPPVDD for IO181A16_CCLKBPBCU4A16-bit PC Card Address/CLK182A14_nCPERRBUPBCU4A16-bit PC Card Address/CRDY183A14_nCPERRBUPBCU4A16-bit PC Card Address/CRPR184A13_CPARBUPBCU4A16-bit PC Card Address/CARB185A12_nCGE2BUPBCU4A16-bit PC Card Address/CardBus Address Data186A10_CADPBUPBCU4A16-bit PC Card Address/CardBus Address Data188AA1_CAD12BUPBCU4A16-bit PC Card Address/CardBus Address Data188AA1_CAD14BUPBCU4A16-bit PC Card Address/CardBus Address Data188AA1_CAD24BUPBCU4A16-bit PC Card Address/CardBus Address Data188AA1_CAD24BUPBCU4A16-bit PC Card Address/CardBus Address Data189AA_CAD24BUPBCU4A16-bit PC Card Address/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 171 | A24_CAD17      | BU | PBCU4A | 16-bit PC Card Address/CardBus Address Data                     |

| NAT         NAT         BU         PBCU4A         16-bit PC Card Address/CardBus TRDY           175         A21_nCDEVSEL         BU         PBCU4A         16-bit PC Card Address/CardBus Dev Sel           176         A20_nCSTOP         BU         PBCU4A         16-bit PC Card Address/CardBus CBLOCK           177         A19_nCBLOCK         BU         PBCU4A         16-bit PC Card Address/CardBus Address Data           179         A17_CAD16         BU         PBCU4A         16-bit PC Card Address/CardBus Address Data           180         VCCP         P         VDD for IO           181         A16_CCLK         B         PBCU4A         16-bit PC Card Address/CBR           182         A14_nCPERR         BU         PBCU4A         16-bit PC Card Address/CBRY           183         A14_nCPERR         BU         PBCU4A         16-bit PC Card Address/CBR           184         A13_CPAR         BU         PBCU4A         16-bit PC Card Address/CBRR           185         A12_nCCBE2         BU         PBCU4A         16-bit PC Card Address/CardBus Address Data           186         A12_nCAD12         BU         PBCU4A         16-bit PC Card Address/CardBus Address Data           187         A11_CAD12         BU         PBCU4A         16-bit PC Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 172 | VSSP           | Р  |        | VSS for IO                                                      |

| A21_nCDEVSEL         BU         PBCU4A         16-bit PC Card Address/CardBus Dev Sel           176         A20_nCSTOP         BU         PBCU4A         16-bit PC Card Address/CardBus STOP           177         A19_nCBLOCK         BU         PBCU4A         16-bit PC Card Address/CardBus CBLOCK           178         A18         B         PBCU4A         16-bit PC Card Address/CardBus Address Data           178         A17_CAD16         BU         PBCU4A         16-bit PC Card Address/CardBus Address Data           179         A17_CAD16         BU         PBCU4A         16-bit PC Card Address/CardBus Address Data           180         VCCP         P         VDD for IO         VDD for IO           181         A16_nCLK         B         PBCU4A         16-bit PC Card Address/CLK           182         A15_nCIRDY         BU         PBCU4A         16-bit PC Card Address/CPRR           183         A14_nCPERR         BU         PBCU4A         16-bit PC Card Address/CardBus Address Data           184         A13_cPAR         BU         PBCU4A         16-bit PC Card Address/CardBus Address Data           185         A12_nCCBE2         BU         PBCU4A         16-bit PC Card Address/CardBus Address Data           186         A10_cAD12         BU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 173 | A23_nCFRAME    | BU | PBCU4A | 16-bit PC Card Address/CardBus Frame                            |

| 176A20_nCSTOPBUPBCU4A16-bit PC Card Address/CardBus STOP177A19_nCBLOCKBUPBCU4A16-bit PC Card Address/CardBus CBLOCK178A18_mBPBCU4A16-bit PC Card Address/CardBus Address Data179A17_CAD16BUPBCU4A16-bit PC Card Address/CardBus Address Data180VCCPPVD for IO181A16_CCLKBPBCU4A16-bit PC Card Address/CLK182A15_nCIRDYBUPBCU4A16-bit PC Card Address/CLK183A14_nCPERRBUPBCU4A16-bit PC Card Address/CRDY184A13_CPARBUPBCU4A16-bit PC Card Address/CCBE2186A12_nCCBE2BUPBCU4A16-bit PC Card Address/CCBE2186A12_nCCBE2BUPBCU4A16-bit PC Card Address/CCBE2187A11_CAD12BUPBCU4A16-bit PC Card Address/CardBus Address Data188A0_CAD2BUPBCU4A16-bit PC Card Address/CardBus Address Data189A9_CAD14BUPBCU4A16-bit PC Card Address/CardBus Address Data190A8_nCCBE1BUPBCU4A16-bit PC Card Address/CardBus Address Data191A7_CAD18BUPBCU4A16-bit PC Card Address/CardBus Address Data192A6_CAD20BUPBCU4A16-bit PC Card Address/CardBus Address Data193VSSPPVSS for IO194A4_CAD22BUPBCU4A16-bit PC Card Address/CardBus Address Data195A4_CAD23BU<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 174 | A22_nCTRDY     | BU | PBCU4A | 16-bit PC Card Address/CardBus TRDY                             |

| 177A19_nCBLOCKBUPBCU4A16-bit PC Card Address/CardBus CBLOCK178A18BPBC4A16-bit PC Card Address/CardBus Address Data179A17_GAD16BUPBCU4A16-bit PC Card Address/CardBus Address Data180VCCPPVDD for IO181A16_CCLKBPBC4A16-bit PC Card Address/CardBus Address Data182A15_nCIRDYBUPBCU4A16-bit PC Card Address/CIRDY183A14_nCPERRBUPBCU4A16-bit PC Card Address/CPER184A13_CPARBUPBCU4A16-bit PC Card Address/CDE2185A12_nCCBE2BUPBCU4A16-bit PC Card Address/CCBE2186VCCIPVDD for core187A11_GAD12BUPBCU4A16-bit PC Card Address/CardBus Address Data188A10_CAD9BUPBCU4A16-bit PC Card Address/CardBus Address Data189A9_CAD14BUPBCU4A16-bit PC Card Address/CardBus Address Data190A8_nCCBE1BUPBCU4A16-bit PC Card Address/CardBus Address Data191A7_CAD18BUPBCU4A16-bit PC Card Address/CardBus Address Data192A6_CAD20BUPBCU4A16-bit PC Card Address/CardBus Address Data193A4_CAD22BUPBCU4A16-bit PC Card Address/CardBus Address Data194A5_CAD20BUPBCU4A16-bit PC Card Address/CardBus Address Data195A4_CAD22BUPBCU4A16-bit PC Card Address/CardBus Address Data <tr< td=""><td>175</td><td>A21_nCDEVSEL</td><td>BU</td><td>PBCU4A</td><td>16-bit PC Card Address/CardBus Dev Sel</td></tr<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 175 | A21_nCDEVSEL   | BU | PBCU4A | 16-bit PC Card Address/CardBus Dev Sel                          |

| A18         B         PBC4A         16-bit PC Card Address           179         A17_CAD16         BU         PBCU4A         16-bit PC Card Address/CardBus Address Data           180         VCCP         P         VD for IO           181         A16_CCLK         B         PBC9A         16-bit PC Card Address/CardBus Address Data           182         A15_nCIRDY         BU         PBC04A         16-bit PC Card Address/CLK           183         A14_nCPERR         BU         PBC04A         16-bit PC Card Address/CPRR           184         A13_CPAR         BU         PBC04A         16-bit PC Card Address/CPRR           184         A13_CPAR         BU         PBC04A         16-bit PC Card Address/CPRR           185         A12_nCCBE2         BU         PBC04A         16-bit PC Card Address/CBE2           186         A10_CAD12         BU         PBC04A         16-bit PC Card Address/CardBus Address Data           187         A11_CAD12         BU         PBC04A         16-bit PC Card Address/CardBus Address Data           188         A10_CAD9         BU         PBC04A         16-bit PC Card Address/CardBus Address Data           199         A8_nCCBE1         BU         PBC04A         16-bit PC Card Address/CardBus Address Data <t< td=""><td>176</td><td>A20_nCSTOP</td><td>BU</td><td>PBCU4A</td><td>16-bit PC Card Address/CardBus STOP</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 176 | A20_nCSTOP     | BU | PBCU4A | 16-bit PC Card Address/CardBus STOP                             |

| 179A17_CAD16BUPBCU4A16-bit PC Card Address/CardBus Address Data180VCCPPVD for IO181A16_CCLKBPBC8A16-bit PC Card Address/CCLK182A15_nCIRDYBUPBCU4A16-bit PC Card Address/CIRDY183A14_nCPERRBUPBCU4A16-bit PC Card Address/CPERR184A13_CPARBUPBCU4A16-bit PC Card Address/CPER185A12_nCCB22BUPBCU4A16-bit PC Card Address/CCB2186VCCIPVD for core187A11_CAD12BUPBCU4A16-bit PC Card Address/CardBus Address Data188A10_CAD9BUPBCU4A16-bit PC Card Address/CardBus Address Data189A9_CAD14BUPBCU4A16-bit PC Card Address/CardBus Address Data190A8_nCCBE1BUPBCU4A16-bit PC Card Address/CardBus Address Data191A7_CAD18BUPBCU4A16-bit PC Card Address/CardBus Address Data192A6_CAD20BUPBCU4A16-bit PC Card Address/CardBus Address Data193VSSPPVSS for IO194A5_CAD21BUPBCU4A16-bit PC Card Address/CardBus Address Data195A4_CAD22BUPBCU4A16-bit PC Card Address/CardBus Address Data196A3_CAD23BUPBCU4A16-bit PC Card Address/CardBus Address Data197A2_CAD24BUPBCU4A16-bit PC Card Address/CardBus Address Data198A4_CAD25BUPBCU4A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 177 | A19_nCBLOCK    | BU | PBCU4A | 16-bit PC Card Address/CardBus CBLOCK                           |

| 180VCCPPVDD for IO181A16_CCLKBPBC8A16-bit PC Card Address/CLK182A15_nCIRDYBUPBCU4A16-bit PC Card Address/CIRDY183A14_nCPERRBUPBCU4A16-bit PC Card Address/CPERR184A13_CPARBUPBCU4A16-bit PC Card Address/CPERR185A12_nCCBE2BUPBCU4A16-bit PC Card Address/CPER186VCCIPVDD for core187A11_CAD12BUPBCU4A16-bit PC Card Address/CardBus Address Data188A10_CAD9BUPBCU4A16-bit PC Card Address/CardBus Address Data189A9_CAD14BUPBCU4A16-bit PC Card Address/CardBus Address Data190A8_nCCBE1BUPBCU4A16-bit PC Card Address/CardBus Address Data191A7_CAD18BUPBCU4A16-bit PC Card Address/CardBus Address Data192A6_CAD20BUPBCU4A16-bit PC Card Address/CardBus Address Data193AS_nCCBE1BUPBCU4A16-bit PC Card Address/CardBus Address Data194A5_CAD21BUPBCU4A16-bit PC Card Address/CardBus Address Data195A4_CAD22BUPBCU4A16-bit PC Card Address/CardBus Address Data196A3_CAD23BUPBCU4A16-bit PC Card Address/CardBus Address Data197A2_CAD24BUPBCU4A16-bit PC Card Address/CardBus Address Data198A4_CAD25BUPBCU4A16-bit PC Card Address/CardBus Address Data1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 178 | A18            | В  | PBC4A  | 16-bit PC Card Address                                          |

| 181A16_CCLKBPBC8A16-bit PC Card Address/CLK182A15_nCIRDYBUPBCU4A16-bit PC Card Address/CIRDY183A14_nCPERRBUPBCU4A16-bit PC Card Address/CPERR184A13_CPARBUPBCU4A16-bit PC Card Address/CPAR185AA12_nCCBE2BUPBCU4A16-bit PC Card Address/CCBE2186VCCIPVDD for core187A11_CAD12BUPBCU4A16-bit PC Card Address/CardBus Address Data188A10_CAD9BUPBCU4A16-bit PC Card Address/CardBus Address Data189AA9_CAD14BUPBCU4A16-bit PC Card Address/CardBus Address Data190A8_nCCBE1BUPBCU4A16-bit PC Card Address/CardBus Address Data191A7_CAD18BUPBCU4A16-bit PC Card Address/CardBus Address Data192A6_CAD20BUPBCU4A16-bit PC Card Address/CardBus Address Data193AS_CAD21BUPBCU4A16-bit PC Card Address/CardBus Address Data194A4_CAD22BUPBCU4A16-bit PC Card Address/CardBus Address Data195A4_CAD24BUPBCU4A16-bit PC Card Address/CardBus Address Data196A4_CAD24BUPBCU4A16-bit PC Card Address/CardBus Address Data195A4_CAD24BUPBCU4A16-bit PC Card Address/CardBus Address Data196A4_CAD25BUPBCU4A16-bit PC Card Address/CardBus Address Data197A4_CAD26BUPBCU4A16-bit P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 179 | A17_CAD16      | BU | PBCU4A | 16-bit PC Card Address/CardBus Address Data                     |

| 182A15_nCIRDYBUPBCU4A16-bit PC Card Address/CIRDY183A14_nCPERRBUPBCU4A16-bit PC Card Address/CPERR184A13_CPARBUPBCU4A16-bit PC Card Address/CPAR185A12_nCCBE2BUPBCU4A16-bit PC Card Address/CBE2186VCCIPVD for core187A11_CAD12BUPBCU4A16-bit PC Card Address/CardBus Address Data188A10_CAD9BUPBCU4A16-bit PC Card Address/CardBus Address Data189A9_CAD14BUPBCU4A16-bit PC Card Address/CardBus Address Data190A8_nCCBE1BUPBCU4A16-bit PC Card Address/CardBus Address Data191A7_CAD18BUPBCU4A16-bit PC Card Address/CardBus Address Data192A6_CAD20BUPBCU4A16-bit PC Card Address/CardBus Address Data193VSSPPVSS for IO194A5_CAD21BUPBCU4A16-bit PC Card Address/CardBus Address Data195A4_CAD22BUPBCU4A16-bit PC Card Address/CardBus Address Data196A3_CAD23BUPBCU4A16-bit PC Card Address/CardBus Address Data197A2_CAD24BUPBCU4A16-bit PC Card Address/CardBus Address Data198A1_CAD25BUPBCU4A16-bit PC Card Address/CardBus Address Data199A0_CAD26BUPBCU4A16-bit PC Card Address/CardBus Address Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 180 | VCCP           | Р  |        | VDD for IO                                                      |

| 183AA14_nCPERRBUPBCU4A16-bit PC Card Address/CPERR184A13_CPARBUPBCU4A16-bit PC Card Address/CPAR185A12_nCCBE2BUPBCU4A16-bit PC Card Address/CCBE2186VCCIPVDD for core187A11_CAD12BUPBCU4A16-bit PC Card Address/CardBus Address Data188A10_CAD9BUPBCU4A16-bit PC Card Address/CardBus Address Data189A9_CAD14BUPBCU4A16-bit PC Card Address/CardBus Address Data190A8_nCCBE1BUPBCU4A16-bit PC Card Address/CardBus Address Data191A7_CAD18BUPBCU4A16-bit PC Card Address/CardBus Address Data192A6_CAD20BUPBCU4A16-bit PC Card Address/CardBus Address Data193VSSPPVSS for IO194A5_CAD21BUPBCU4A16-bit PC Card Address/CardBus Address Data195A4_CAD22BUPBCU4A16-bit PC Card Address/CardBus Address Data196A3_CAD23BUPBCU4A16-bit PC Card Address/CardBus Address Data197A2_CAD24BUPBCU4A16-bit PC Card Address/CardBus Address Data198A1_CAD25BUPBCU4A16-bit PC Card Address/CardBus Address Data199A0_CAD26BUPBCU4A16-bit PC Card Address/CardBus Address Data198A1_CAD25BUPBCU4A16-bit PC Card Address/CardBus Address Data199A0_CAD26BUPBCU4A16-bit PC Card Address/CardBus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 181 | A16_CCLK       | В  | PBC8A  | 16-bit PC Card Address/CCLK                                     |

| 184A13_CPARBUPBCU4A16-bit PC Card Address/CPAR185A12_nCCBE2BUPBCU4A16-bit PC Card Address/CCBE2186VCCIPVDD for core187A11_CAD12BUPBCU4A16-bit PC Card Address/CardBus Address Data188A10_CAD9BUPBCU4A16-bit PC Card Address/CardBus Address Data189A9_CAD14BUPBCU4A16-bit PC Card Address/CardBus Address Data190A8_nCCBE1BUPBCU4A16-bit PC Card Address/CardBus Address Data191A7_CAD18BUPBCU4A16-bit PC Card Address/CardBus Address Data192A6_CAD20BUPBCU4A16-bit PC Card Address/CardBus Address Data193VSSPPVSS for IO194A5_CAD21BUPBCU4A16-bit PC Card Address/CardBus Address Data195A4_CAD22BUPBCU4A16-bit PC Card Address/CardBus Address Data196A3_CAD23BUPBCU4A16-bit PC Card Address/CardBus Address Data197A2_CAD24BUPBCU4A16-bit PC Card Address/CardBus Address Data198A1_CAD25BUPBCU4A16-bit PC Card Address/CardBus Address Data199A0_CAD26BUPBCU4A16-bit PC Card Address/CardBus Address Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 182 | A15_nCIRDY     | BU | PBCU4A | 16-bit PC Card Address/CIRDY                                    |